# **MAX II Device Handbook**

101 Innovation Drive San Jose, CA 95134 www.altera.com

MII5V1-3.3

Copyright © 2009 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products any time without notice. Altera aspecifications or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Contents**

| Chapter Revision Dates                     | xi  |

|--------------------------------------------|-----|

| About this Handbook                        |     |

| Typographic Conventions                    |     |

| Section I. MAX II Device Family Data Sheet |     |

| Revision History                           | I–1 |

| Chapter 1. Introduction                    |     |

| Introduction                               |     |

| Features                                   | 1–1 |

| Referenced Documents                       |     |

| Document Revision History                  | 1–4 |

| Chapter 2. MAX II Architecture             |     |

| Introduction                               |     |

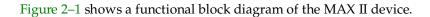

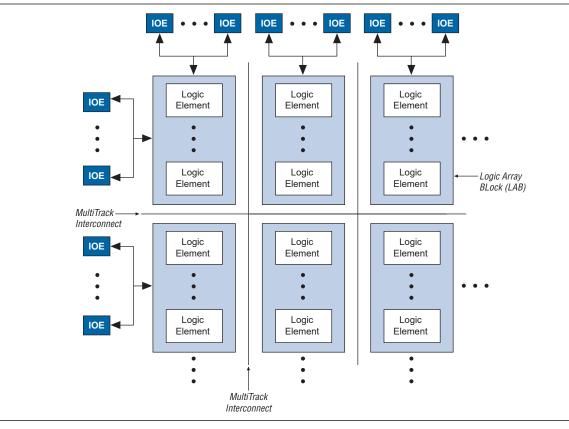

| Functional Description                     |     |

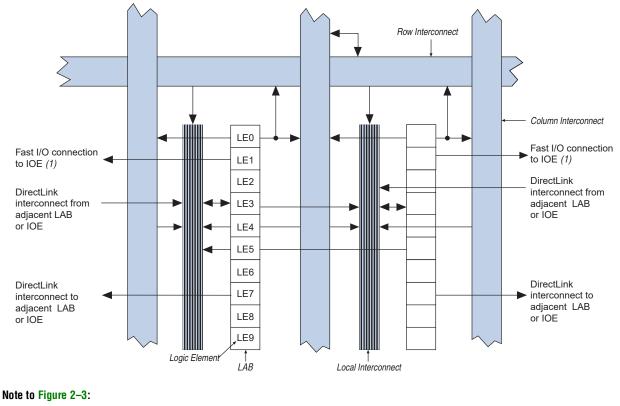

| Logic Array Blocks                         |     |

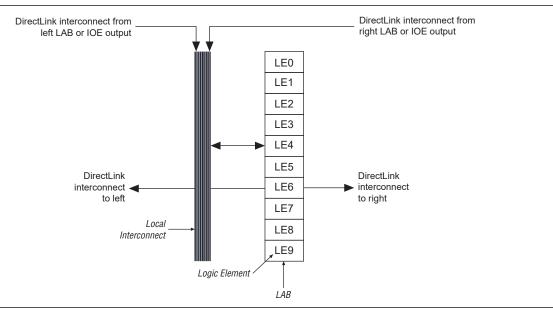

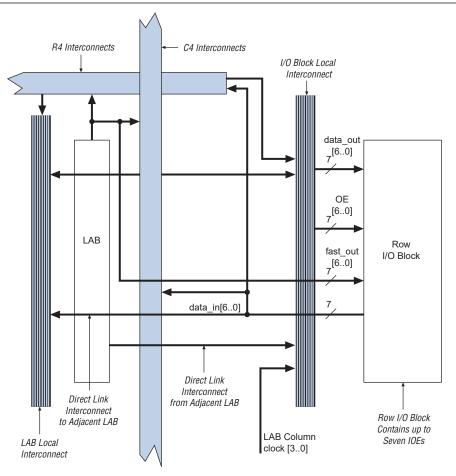

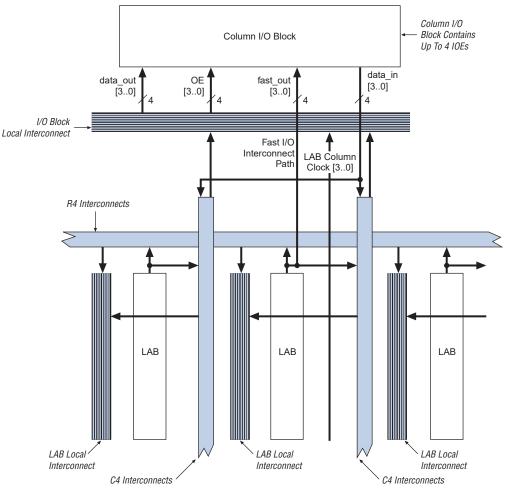

| LAB Interconnects                          |     |

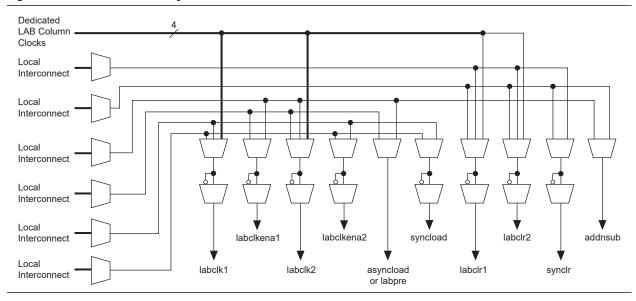

| LAB Control Signals                        |     |

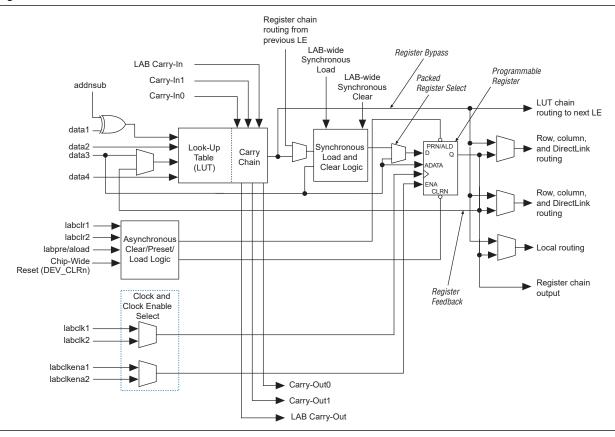

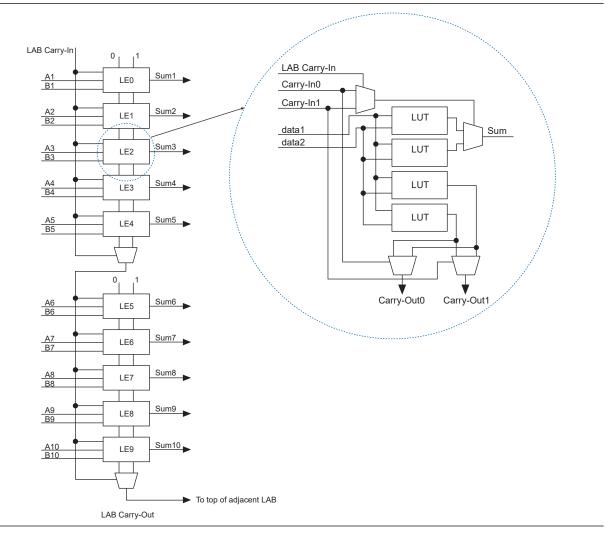

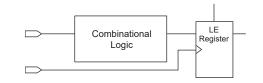

| Logic Elements                             |     |

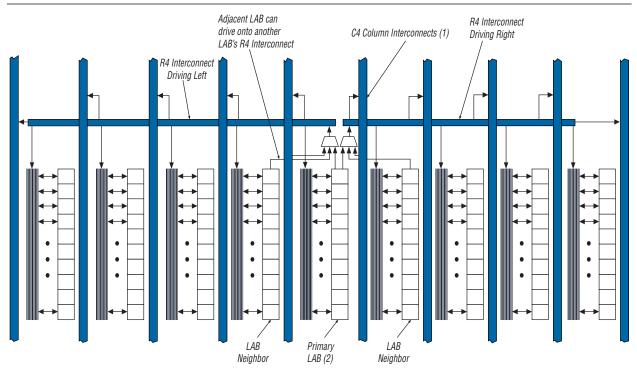

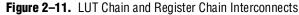

| LUT Chain and Register Chain               |     |

| addnsub Signal                             |     |

| LE Operating Modes                         |     |

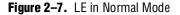

| Normal Mode                                |     |

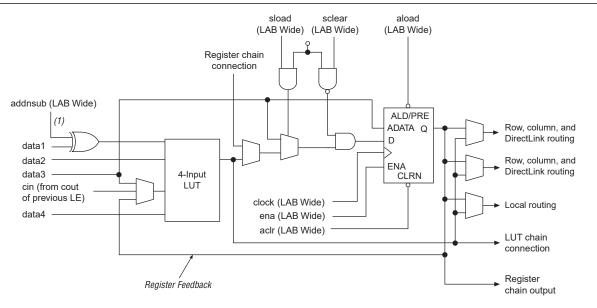

| Dynamic Arithmetic Mode                    |     |

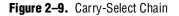

| Carry-Select Chain                         |     |

| Clear and Preset Logic Control             |     |

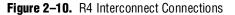

| MultiTrack Interconnect                    |     |

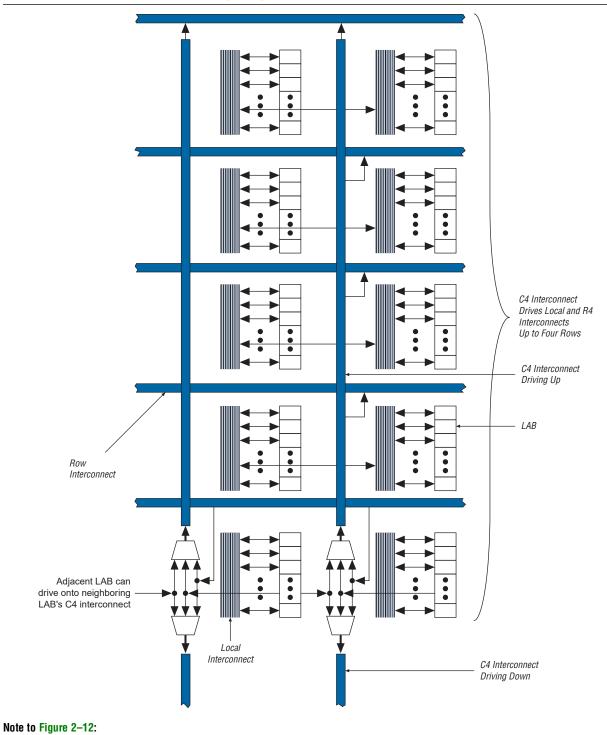

| Global Signals                             |     |

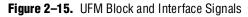

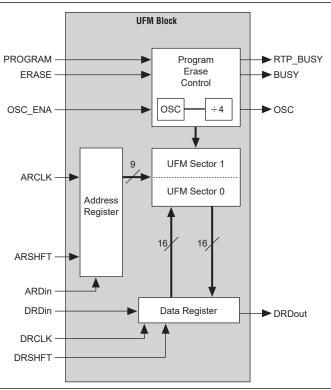

| User Flash Memory Block                    |     |

| UFM Storage                                |     |

| Internal Oscillator                        |     |

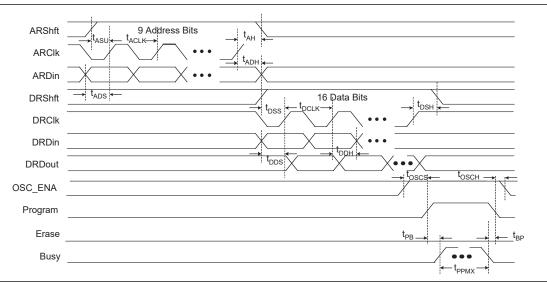

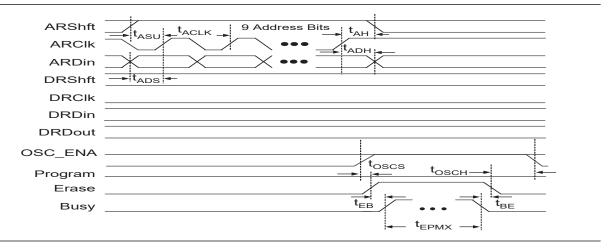

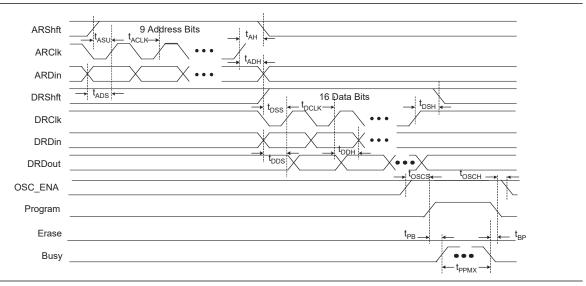

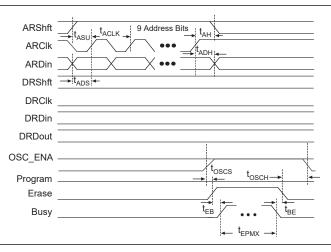

| Program, Erase, and Busy Signals           |     |

| Auto-Increment Addressing                  |     |

| Serial Interface                           |     |

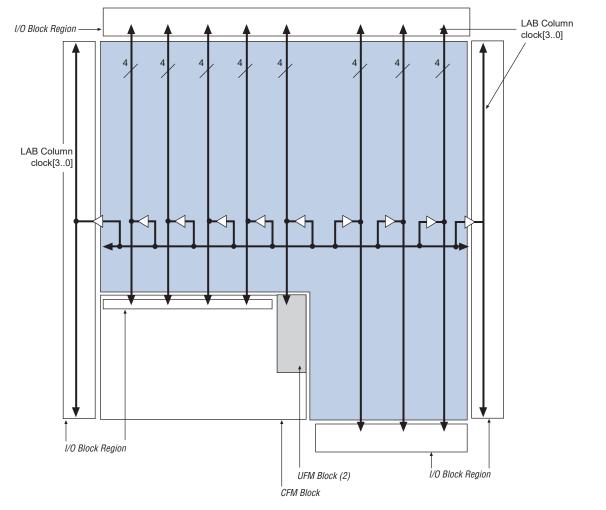

| UFM Block to Logic Array Interface         |     |

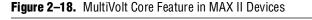

| MultiVolt Core                             |     |

| Fast I/O Connection           |  |

|-------------------------------|--|

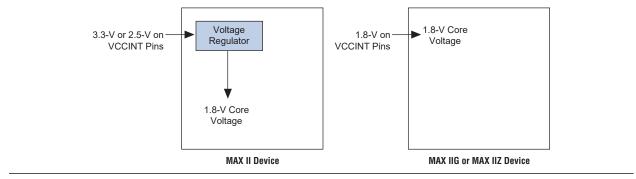

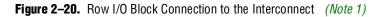

| I/O Blocks                    |  |

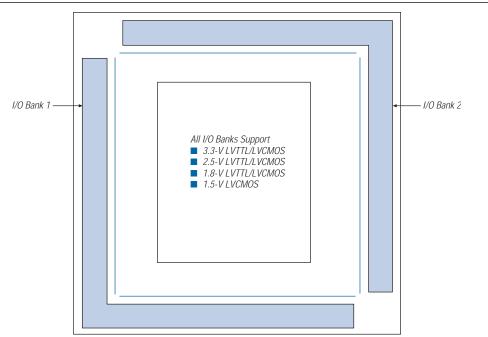

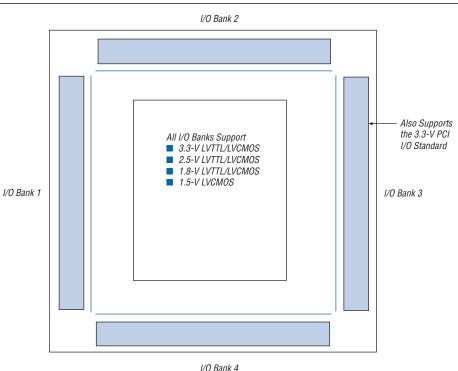

| I/O Standards and Banks       |  |

| PCI Compliance                |  |

| Schmitt Trigger               |  |

| Output Enable Signals         |  |

| Programmable Drive Strength   |  |

| Slew-Rate Control             |  |

| Open-Drain Output             |  |

| Programmable Ground Pins      |  |

| Bus Hold                      |  |

| Programmable Pull-Up Resistor |  |

| Programmable Input Delay      |  |

| MultiVolt I/O Interface       |  |

| Referenced Documents          |  |

| Document Revision History     |  |

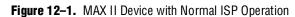

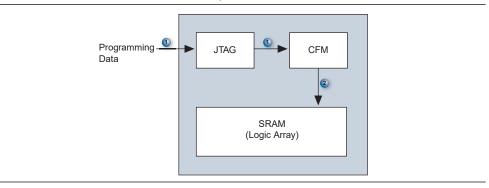

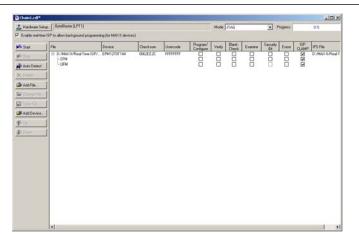

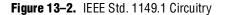

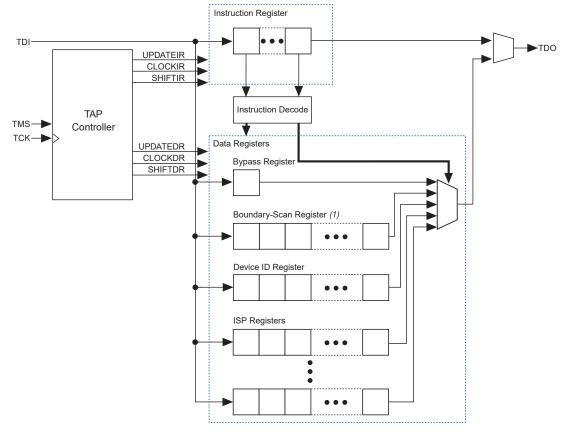

## Chapter 3. JTAG and In-System Programmability

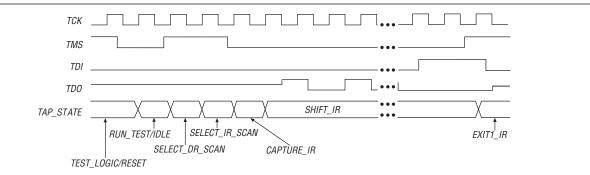

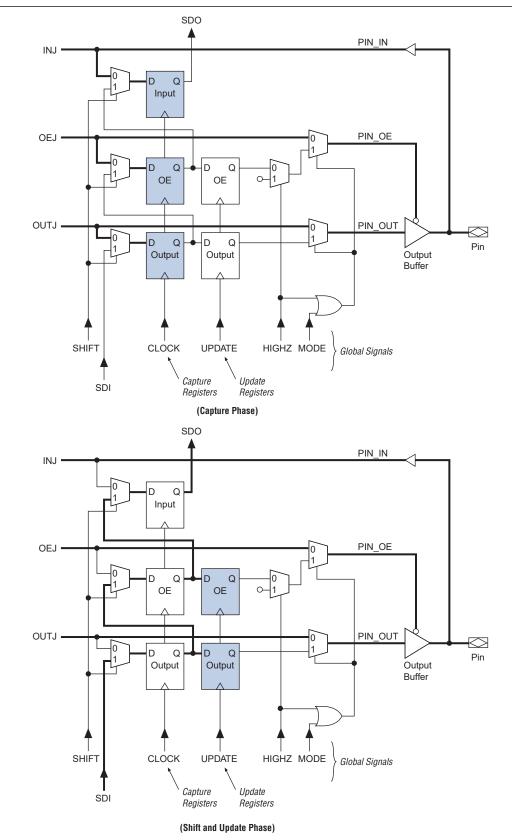

| IEEE Std. 1149.1 (JTAG) Boundary-Scan Support      |    |

|----------------------------------------------------|----|

|                                                    |    |

| JTAG Block                                         | -3 |

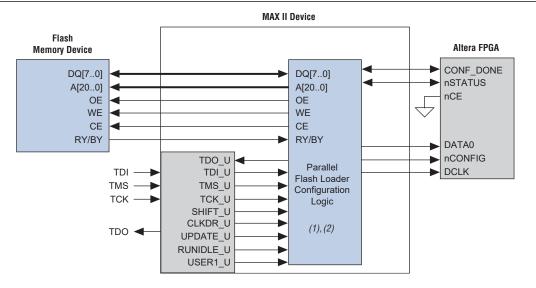

| Parallel Flash Loader                              | -3 |

| In System Programmability                          | -4 |

| IEEE 1532 Support                                  |    |

| Jam Standard Test and Programming Language (STAPL) | -5 |

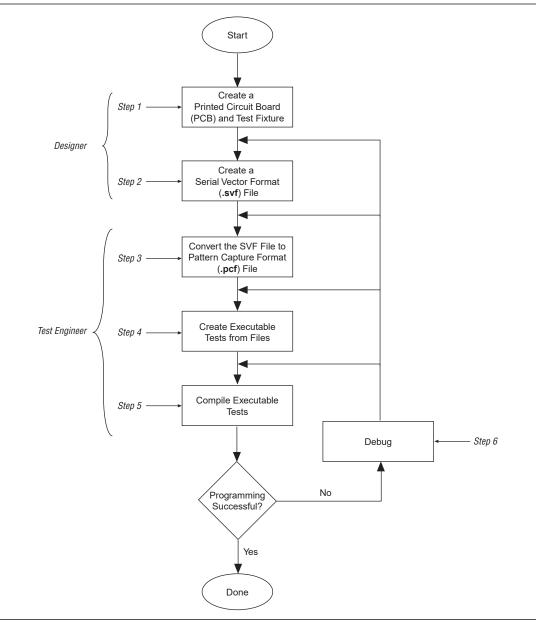

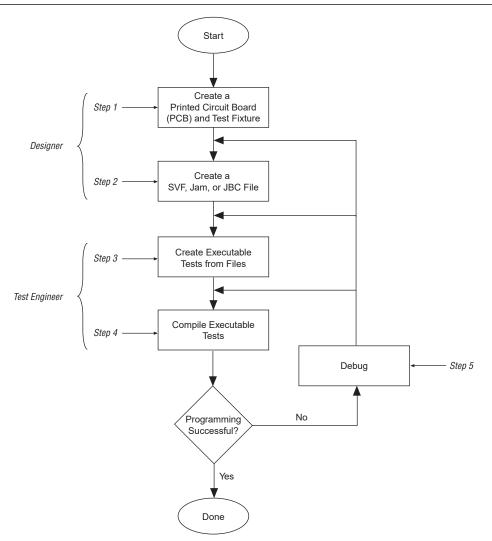

| Programming Sequence                               |    |

| UFM Programming                                    | -6 |

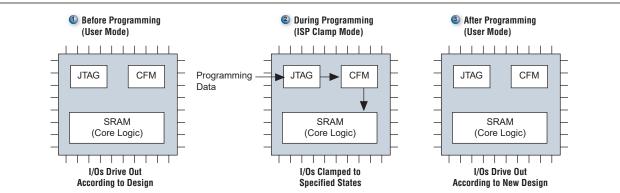

| In-System Programming Clamp                        | -6 |

| Real-Time ISP                                      | -7 |

| Design Security                                    | -7 |

| Programming with External Hardware                 | -7 |

| Referenced Documents                               |    |

| Document Revision History                          | -8 |

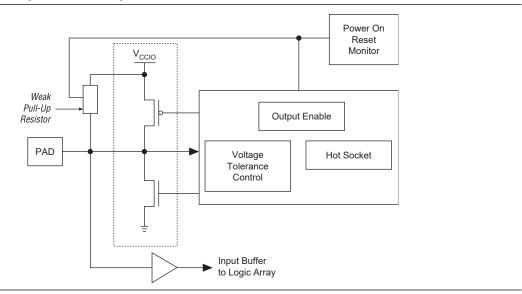

## Chapter 4. Hot Socketing and Power-On Reset in MAX II Devices

| Introduction                                                                        | 4–1 |

|-------------------------------------------------------------------------------------|-----|

| MAX II Hot-Socketing Specifications                                                 | 4–1 |

| Devices Can Be Driven before Power-Up                                               | 4–1 |

| I/O Pins Remain Tri-Stated during Power-Up                                          |     |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> or V <sub>CCINT</sub> Power Supplies |     |

| AC and DC Specifications                                                            |     |

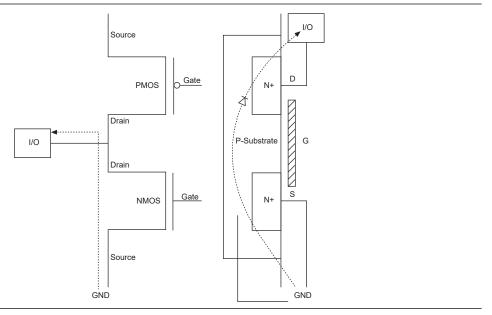

| Hot Socketing Feature Implementation in MAX II Devices                              | 4–2 |

| Power-On Reset Circuitry                                                            |     |

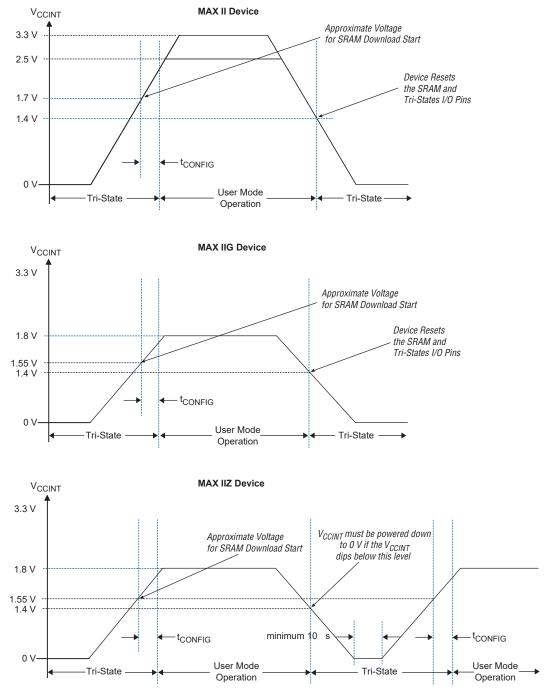

| Power-Up Characteristics                                                            |     |

| Referenced Documents                                                                |     |

| Document Revision History                                                           | 4–8 |

|                                                                                     |     |

## Chapter 5. DC and Switching Characteristics

| uction |

|--------|

|--------|

| Operating Conditions                 | 5–1  |

|--------------------------------------|------|

| Absolute Maximum Ratings             |      |

| Recommended Operating Conditions     |      |

| Programming/Erasure Specifications   |      |

| DC Electrical Characteristics        |      |

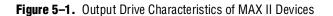

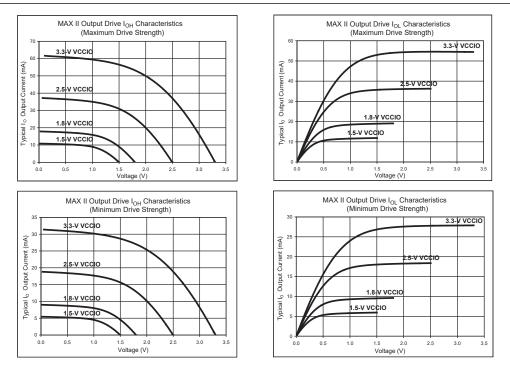

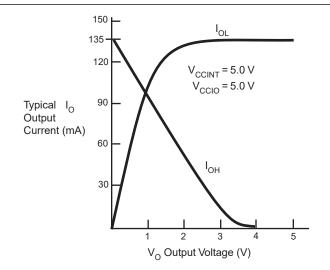

| Output Drive Characteristics         | 5–5  |

| I/O Standard Specifications          | 5–5  |

| Bus Hold Specifications              | 5–7  |

| Power-Up Timing                      | 5–8  |

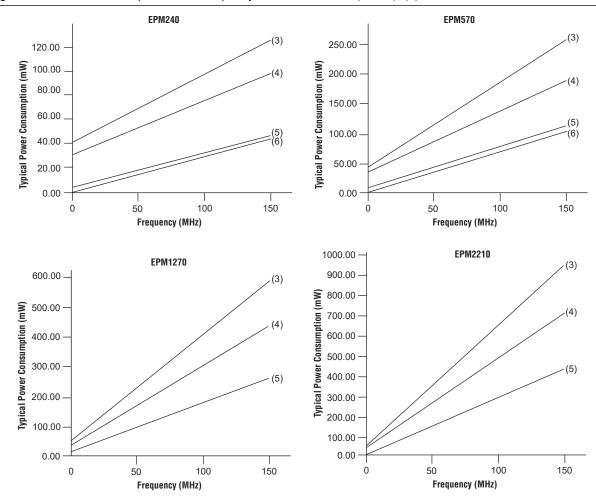

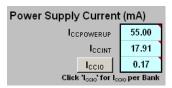

| Power Consumption                    | 5–8  |

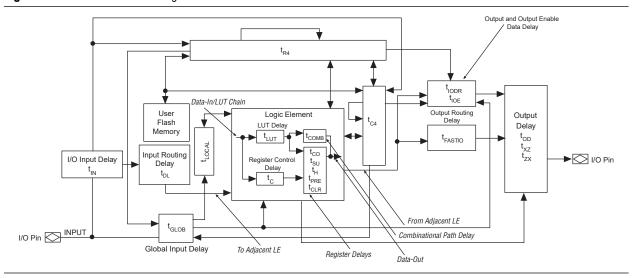

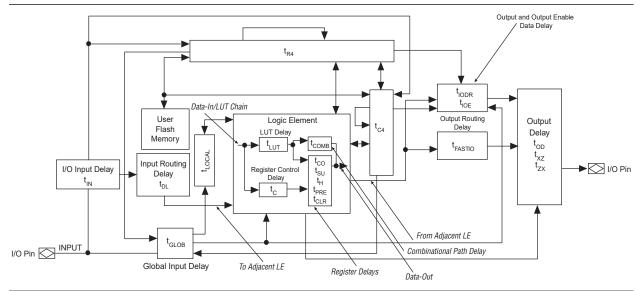

| Timing Model and Specifications      | 5–8  |

| Preliminary and Final Timing         | 5–9  |

| Performance                          | 5–10 |

| Internal Timing Parameters           | 5–11 |

| External Timing Parameters           | 5–18 |

| External Timing I/O Delay Adders     | 5–21 |

| Maximum Input and Output Clock Rates | 5–24 |

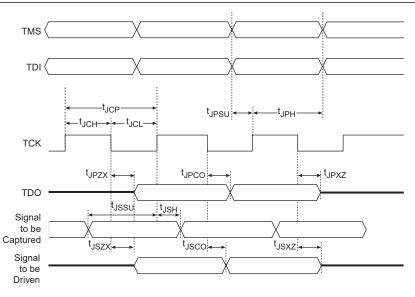

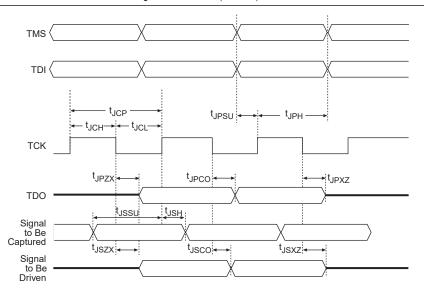

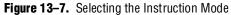

| JTAG Timing Specifications           | 5–25 |

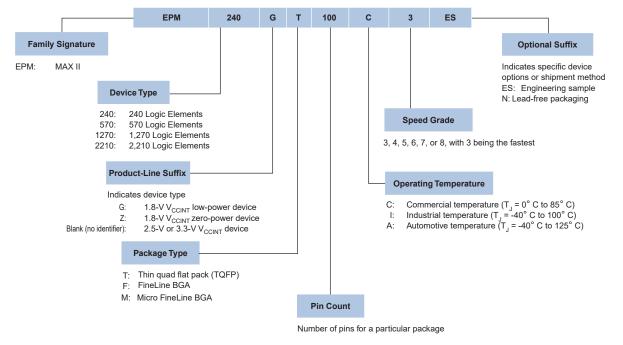

### **Chapter 6. Reference and Ordering Information**

| Software                  | 6–1 |

|---------------------------|-----|

| Device Pin-Outs           | 6–1 |

| Ordering Information      | 6–1 |

| Referenced Documents      | 6–2 |

| Document Revision History | 6–2 |

Referenced Documents

5–26

Document Revision History

5–27

### Section II. PCB Layout Guidelines

| <b>Revision History</b> | ۲ I | [I–1 | - |

|-------------------------|-----|------|---|

|-------------------------|-----|------|---|

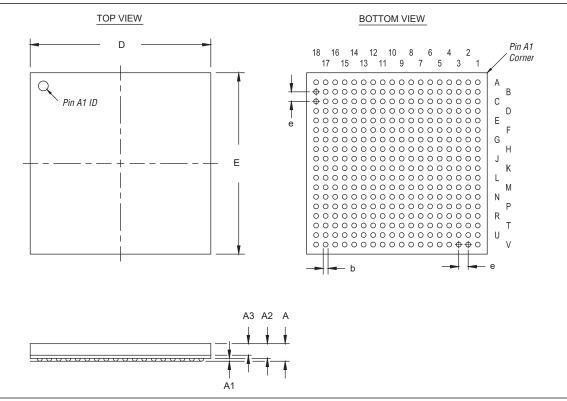

### Chapter 7. Package Information

| Introduction                                              |      |

|-----------------------------------------------------------|------|

| Board Decoupling Guidelines                               | 7–1  |

| Device and Package Cross Reference                        | 7–1  |

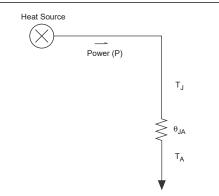

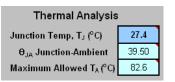

| Thermal Resistance                                        | 7–2  |

| Package Outlines                                          | 7–3  |

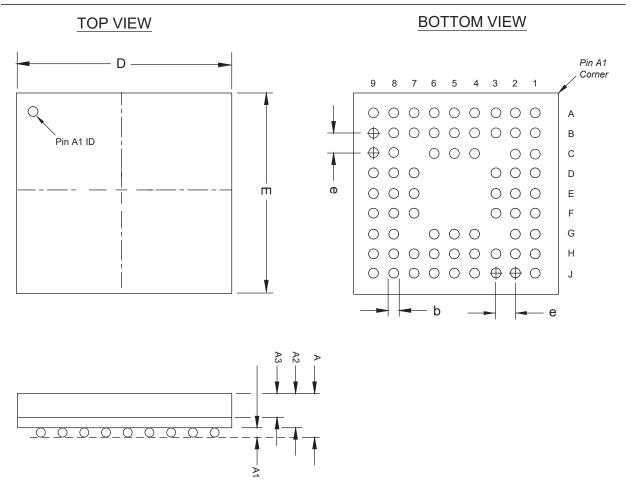

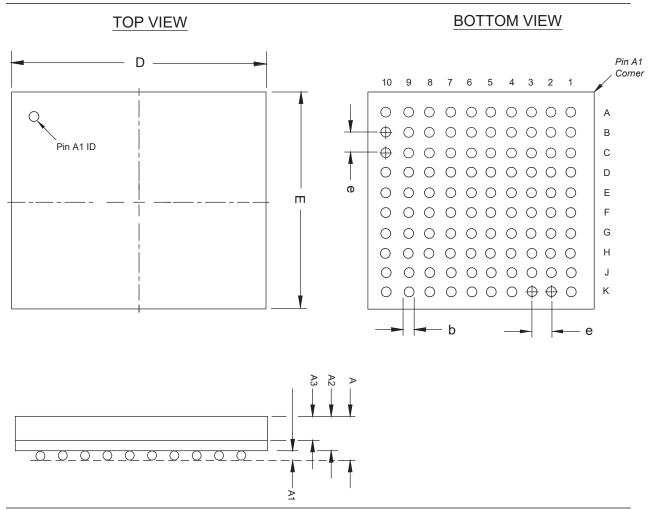

| 68-Pin Micro FineLine Ball-Grid Array (MBGA) – Wire Bond  |      |

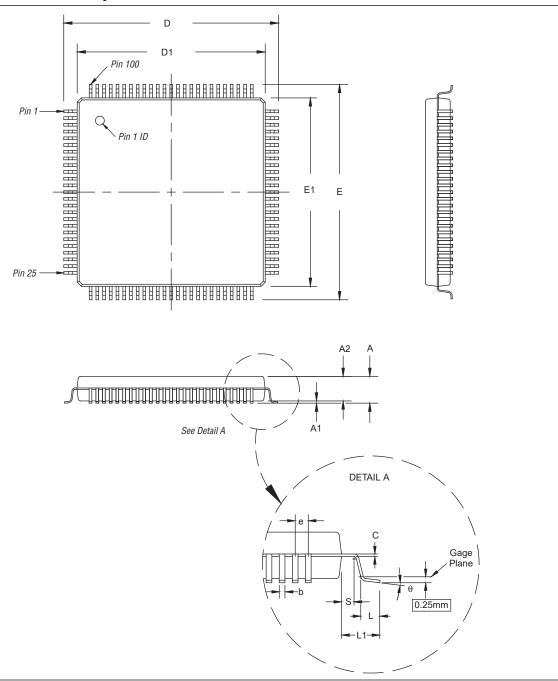

| 100-Pin Plastic Thin Quad Flat Pack (TQFP)                | 7–5  |

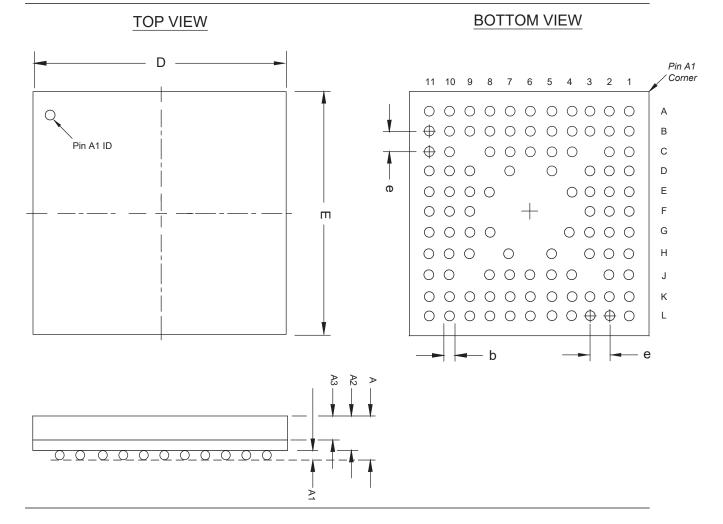

| 100-Pin Micro FineLine Ball-Grid Array (MBGA)             | 7–7  |

| 100-Pin FineLine Ball-Grid Array (FBGA)                   | 7–8  |

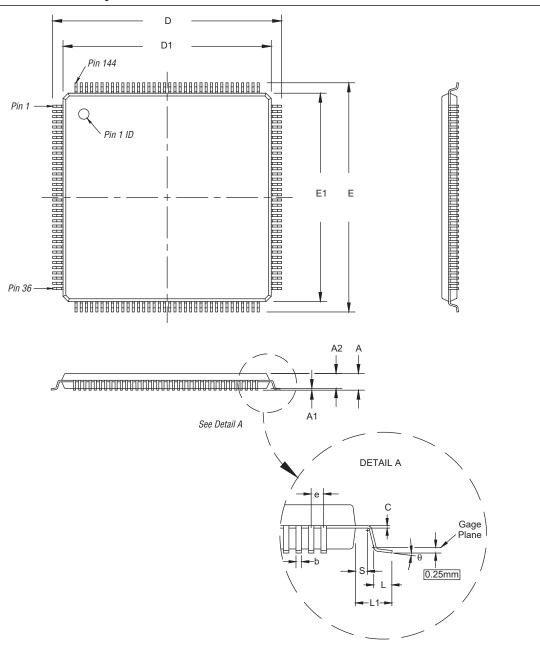

| 144-Pin Plastic Thin Quad Flat Pack (TQFP)                | 7–10 |

| 144-Pin Micro FineLine Ball-Grid Array (MBGA) – Wire Bond | 7–12 |

| 256-Pin Micro FineLine Ball-Grid Array (MBGA)             | 7–13 |

| 256-Pin FineLine Ball-Grid Array (FBGA)                   | 7–15 |

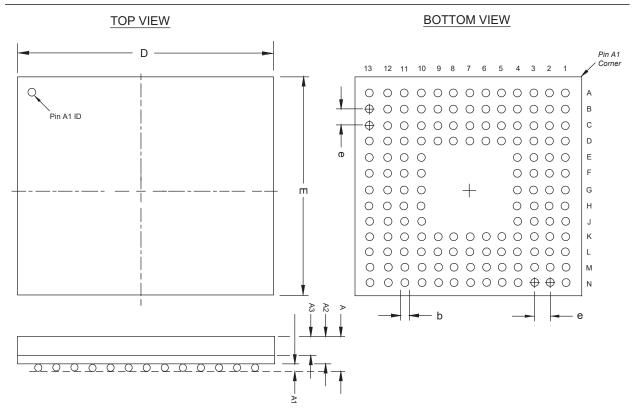

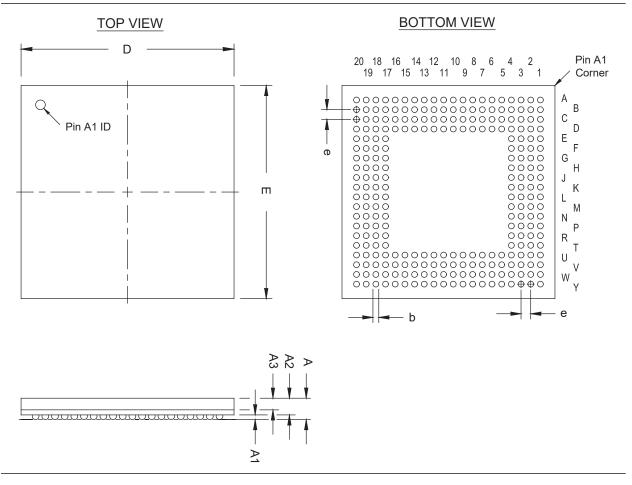

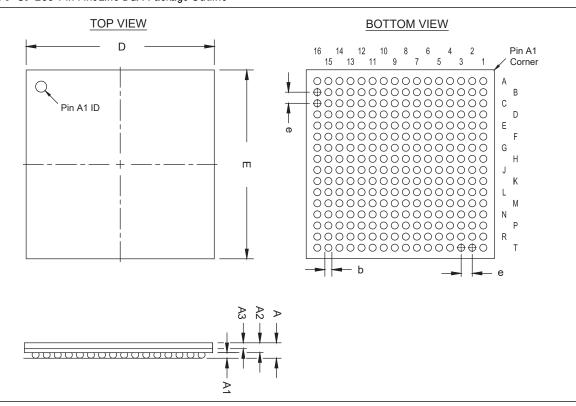

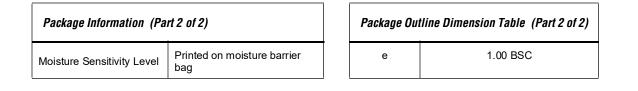

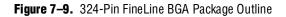

| 324-Pin FineLine Ball-Grid Array (FBGA)                   | 7–16 |

| Document Revision History                                 |      |

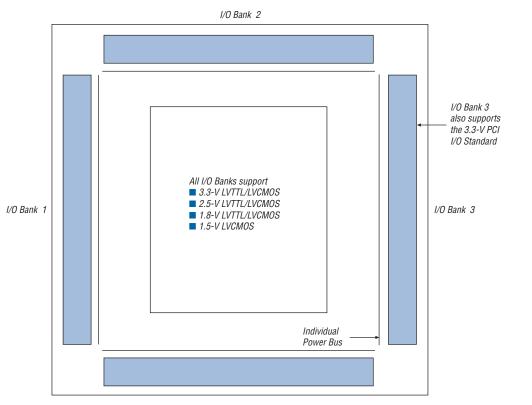

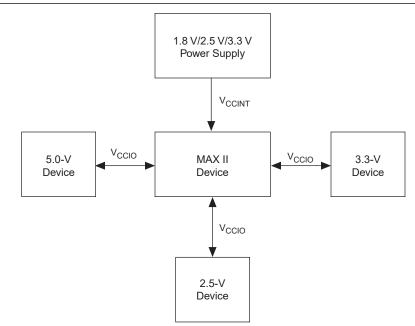

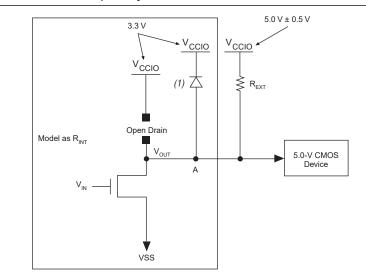

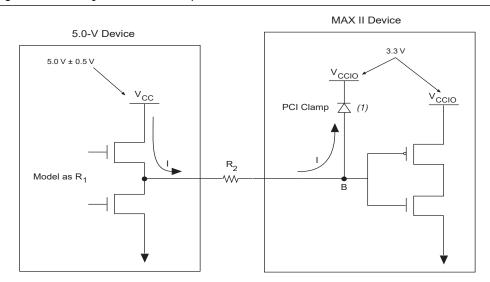

### Chapter 8. Using MAX II Devices in Multi-Voltage Systems

| Introduction                     | -1 |

|----------------------------------|----|

| I/O Standards                    | -2 |

| MultiVolt Core and I/O Operation | -3 |

| 5.0-V Device Compatibility       | -3 |

| Recommended Operating Condition for 5.0-V Compatibility                  |        |

|--------------------------------------------------------------------------|--------|

| Hot Socketing                                                            |        |

| Power-Up Sequencing                                                      | . 8–8  |

| Power-On Reset                                                           | . 8–8  |

| Conclusion                                                               | . 8–8  |

| Referenced Documents                                                     |        |

| Document Revision History                                                |        |

|                                                                          | .0 )   |

| Section III. User Flash Memory                                           |        |

| Revision History                                                         | ΠΙ 1   |

| Revision History                                                         | 111-1  |

|                                                                          |        |

| Chapter 9. Using User Flash Memory in MAX II Devices                     |        |

| Introduction                                                             |        |

| UFM Array Description                                                    |        |

| Memory Organization Map                                                  |        |

| Using and Accessing UFM Storage                                          |        |

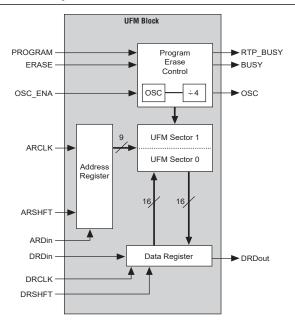

| UFM Functional Description                                               | . 9–3  |

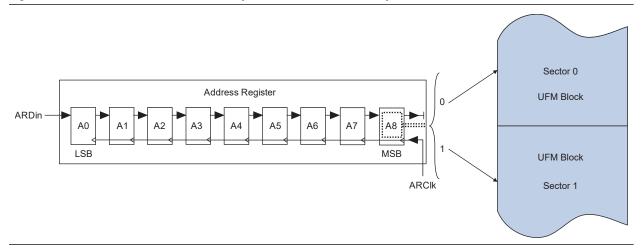

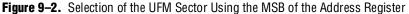

| UFM Address Register                                                     | . 9–5  |

| UFM Data Register                                                        | . 9–5  |

| UFM Program/Erase Control Block                                          |        |

| Oscillator                                                               |        |

| Instantiating the Oscillator without the UFM                             |        |

| UFM Operating Modes                                                      |        |

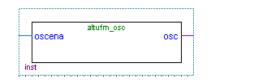

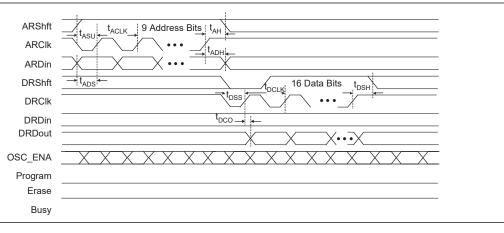

| Read/Stream Read                                                         |        |

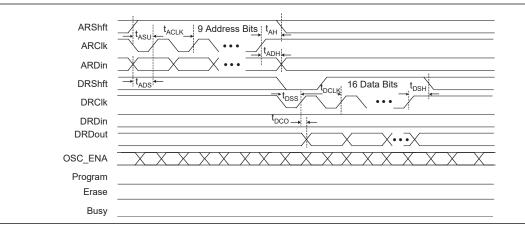

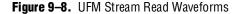

| Program                                                                  |        |

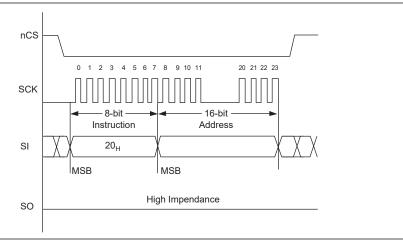

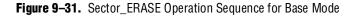

| Erase                                                                    |        |

| Programming and Reading the UFM with JTAG                                |        |

| Jam Files                                                                |        |

| Jam Players                                                              |        |

| Software Support for UFM Block                                           |        |

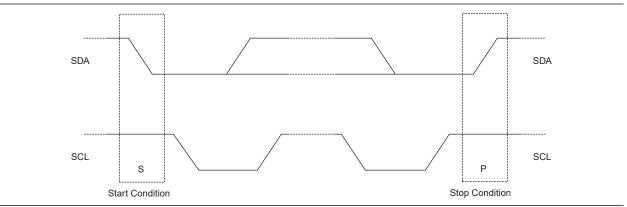

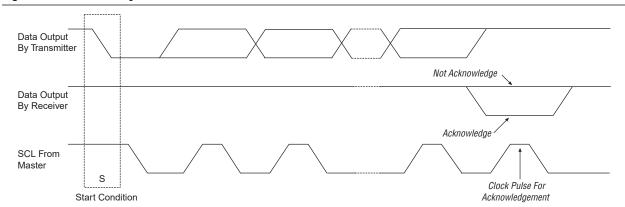

| Inter-Integrated Circuit                                                 |        |

| I <sup>2</sup> C Protocol                                                |        |

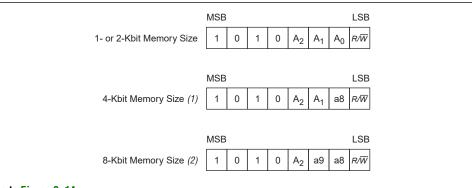

| Device Addressing                                                        |        |

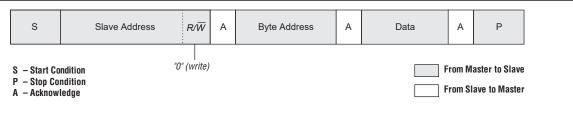

| Byte Write Operation                                                     |        |

| Page Write Operation                                                     |        |

|                                                                          |        |

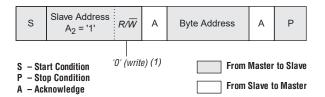

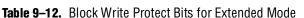

| Write Protection                                                         |        |

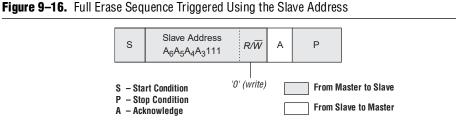

| Erase Operation                                                          |        |

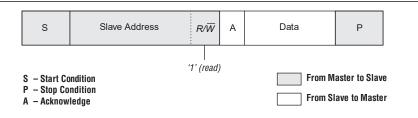

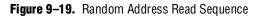

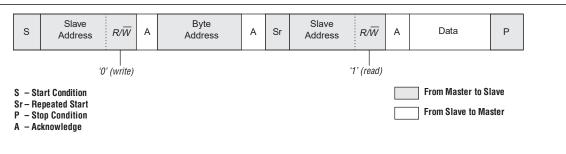

| Read Operation                                                           |        |

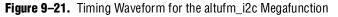

| ALTUFM I <sup>2</sup> C Interface Timing Specification                   | 9-22   |

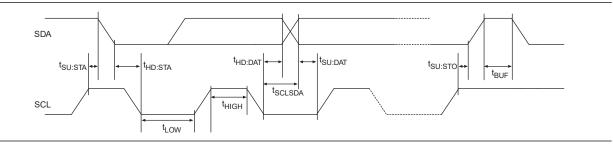

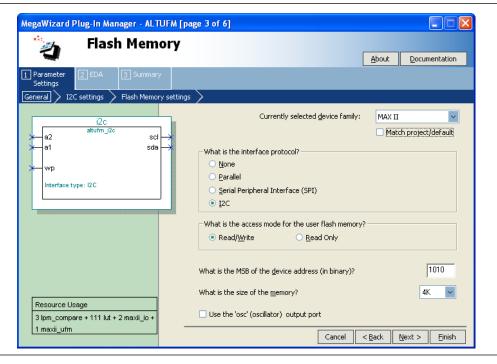

| Instantiating the I2C Interface Using the Quartus II altufm Megafunction |        |

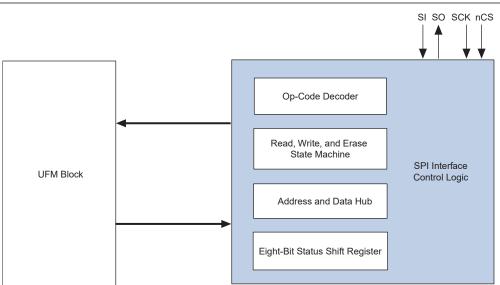

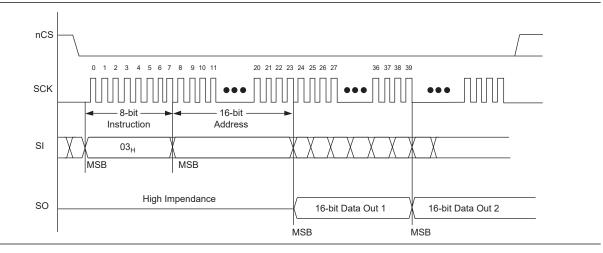

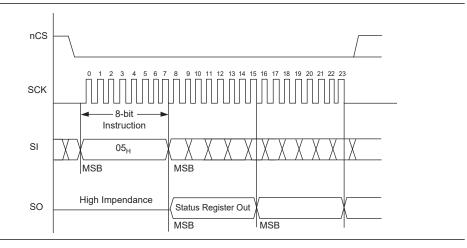

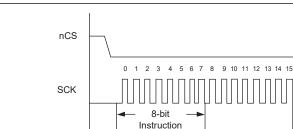

| Serial Peripheral Interface                                              |        |

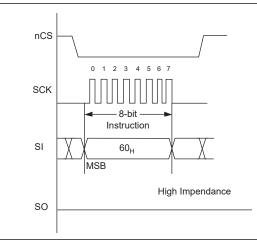

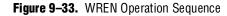

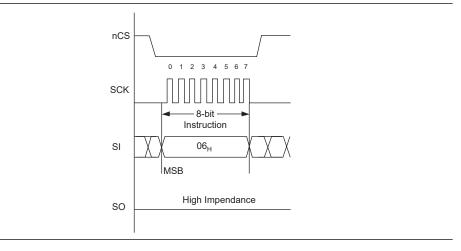

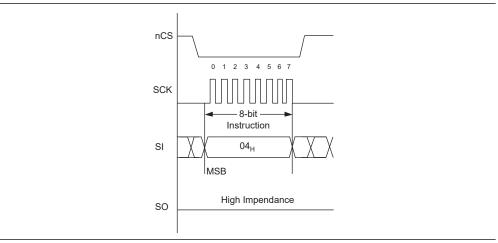

| Opcodes                                                                  |        |

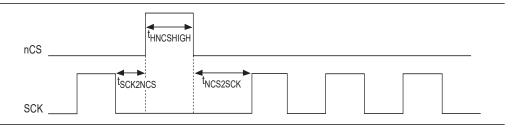

| ALTUFM SPI Timing Specification                                          |        |

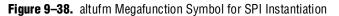

| Instantiating SPI Using Quartus II altufm Megafunction                   |        |

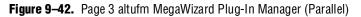

| Parallel Interface                                                       | 9–36   |

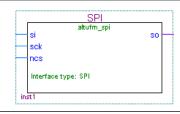

| ALTUFM Parallel Interface Timing Specification                           | . 9–37 |

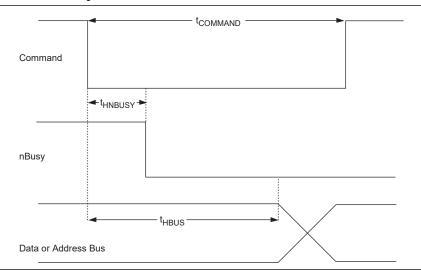

| Instantiating Parallel Interface Using Quartus II altufm Megafunction    |        |

| None (Altera Serial Interface)                                           |        |

| Instantiating None Using Quartus II altufm Megafunction                  |        |

| Creating Memory Content File                                             |        |

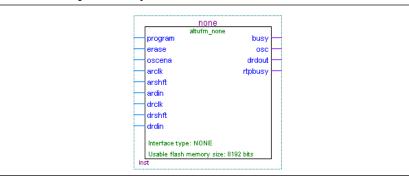

| Memory Initialization for the altufm_parallel Megafunction               |        |

| Memory Initialization for the altufm_spi Megafunction                    |        |

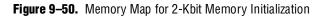

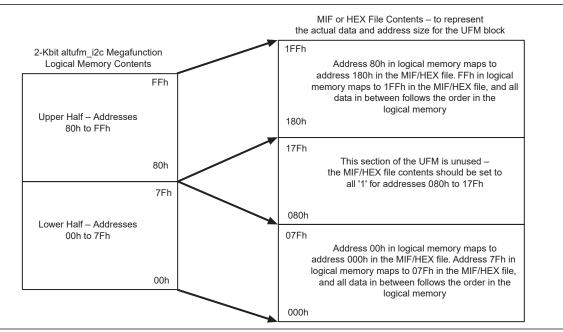

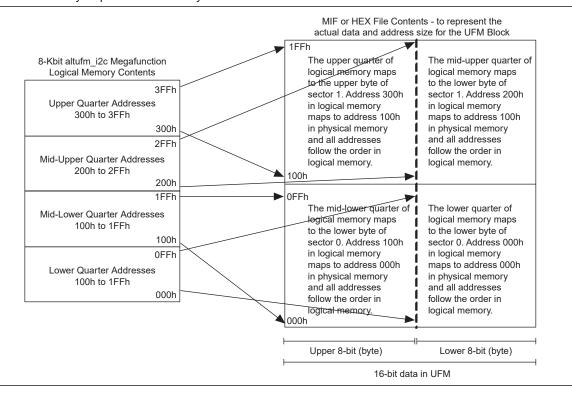

| Memory Initialization for the altufm_i2c Megafunction                    | . 9–44 |

| Simulation Parameters       9-46         Conclusion       9-47         Document Revision History       9-47         Chapter 10. Replacing Serial EEPROMs with MAX II User Flash Memory       10-1         Introduction       10-1         Design Considerations       10-1         List of Vendors and Devices       10-2         Conclusion       10-1         Revision History       10-1         Section IV. In-System Programmability       Revision History         Revision History       IV-1         Chapter 11. In-System Programmability Guidelines for MAX II Devices       11-1         Introduction       11-1         Gondulines       11-1         Operating Conditions       11-1         IsP Voltage       11-2         Interrupting In-System Programming       11-2         Interrupting In-System Programming       11-3         VCDN Operations During In-System Programming       11-3         VCC00 Powered before VCCNN       11-3         VCC00 Powered before VCCNN       11-3         VCC00 Powered before VCCNN       11-4         TCK Signal       11-4         TCK Signal       11-4         TCK Signal       11-4         TCK Signal       1                                                                                                                              |                                                                    |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------|

| Referenced Documents       9–47         Document Revision History       9–47         Chapter 10. Replacing Serial EEPROMs with MAX II User Flash Memory       10–1         Introduction       10–1         Design Considerations       10–1         List of Vendors and Devices       10–2         Conclusion       10–11         Revision History       10–11         Document Revision History       10–12         Section IV. In-System Programmability       Revision History         Section IV. In-System Programmability Guidelines for MAX II Devices       11–1         Introduction       11–1         Operating Conditions       11–1         Input Voltages       11–1         Input Voltages       11–2         IV OPins Tri-Stated during In-System Programming       11–3         V Opins Tri-Stated during In-System Programming       11–4                            |                                                                    |      |

| Document Revision History       9-47         Chapter 10. Replacing Serial EEPROMs with MAX II User Flash Memory       10-1         Design Considerations       10-1         List of Vendors and Devices       10-2         Conclusion       10-11         Referenced Documents       10-11         Document Revision History       10-12         Section IV. In-System Programmability       10-12         Section IV. In-System Programmability Guidelines for MAX II Devices       11-1         Introduction       11-1         General ISP Guidelines       11-1         Operating Conditions       11-1         IsP Voltage       11-2         UFM Operations During In-System Programming       11-3         MultiVolt Devices and Power-Up Sequences       11-3         V <sub>CCO</sub> Powered before V <sub>CCNT</sub> 11-3         J/O Pins Tri-Stated during In-System Programming       11-4         TCK Signal       11-4         PCrogramming via a Download Cable       11-5         Working with Different Voltage Levels       11-4         Programming       11-4         TCK Signal       11-4         Programming via a Download Cable       11-5         Working with Different Voltage Levels       11-6 <t< td=""><td></td><td></td></t<>                                         |                                                                    |      |

| Chapter 10. Replacing Serial EEPROMs with MAX II User Flash Memory       10-1         Introduction       10-1         Design Considerations       10-2         Conclusion       10-11         Referenced Documents       10-11         Document Revision History       10-12         Section IV. In-System Programmability       10-12         Section IV. In-System Programmability Guidelines for MAX II Devices       11-1         Introduction       11-1         General ISP Guidelines       11-1         Operating Conditions       11-1         Introduction       11-1         In Productions       11-1         Introduction       11-1         Introduction       11-1         Introduction       11-1         Introductions       11-1         Introductions       11-2         Interrupting In-System Programming       11-2         Interrupting In-System Programming       11-2         IV Pins Tri-Stated during In-System Programming       11-3         V_Cro Powered before V <sub>CRNT</sub> 11-3         VORing Wi                                                                                                     |                                                                    |      |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Document Revision History                                          |      |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Chapter 10. Replacing Serial EEPROMs with MAX II User Flash Memory |      |

| Design Considerations       10-11         List of Vendors and Devices       10-2         Conclusion       10-11         Referenced Documents       10-11         Document Revision History       10-12         Section IV. In-System Programmability       Revision History         Revision History       IV-1         Chapter 11. In-System Programmability Guidelines for MAX II Devices       Introduction         Introduction       11-1         Operating Conditions       11-1         Input Voltage       11-1         Input Voltage       11-1         Input Voltage       11-2         Interrupting In-System Programming       11-2         Interrupting In-System Programming       11-2         Interrupting In-System Programming       11-3         V Core Powered before V_CONT       11-3         V OP ins Tri-Stated during In-System Programming       11-4         TCK Signal       11-4         Programming via a Download Cable       11-5         Disabling IEEE Std. 1149.1 Circuitry       11-5         Dis Not Conne                                                                                  |                                                                    | 10–1 |

| List of Vendors and Devices       10–2         Conclusion       10–11         Referenced Documents       10–11         Document Revision History       10–12         Section IV. In-System Programmability       10–12         Section IV. In-System Programmability Guidelines for MAX II Devices       11–1         Chapter 11. In-System Programmability Guidelines for MAX II Devices       11–1         General ISP Guidelines       11–1         Operating Conditions       11–1         Introduction       11–1         Input Voltages       11–2         UFM Operations During In-System Programming       11–2         Interrupting In-System Programming       11–3         MultiVolt Devices and Power-Up Sequences       11–3         V <sub>CCD</sub> Powered before V <sub>CCNT</sub> 11–3         I/O Pins Tri-Stated during In-System Programming       11–3         I/O Pins Tri-Stated during In-System Programming       11–4         TCK Signal       11–4         Programming via a Download Cable       11–5         Disabling IEEE Std. 1149.1 Circuitry       11–5         Moreal Vorgamming       11–6         Sequential Programming       11–6         Sequential Programming       11–6         Sequential Programming       11–6 </td <td></td> <td></td>                   |                                                                    |      |

| Conclusion       10–11         Referenced Documents       10–11         Document Revision History       10–12         Section IV. In-System Programmability       Revision History         Revision History       IV–1         Chapter 11. In-System Programmability Guidelines for MAX II Devices       Introduction         Introduction       11–1         General ISP Guidelines       11–1         Operating Conditions       11–1         Isp Voltage       11–1         Input Voltages       11–2         Interduction Buring In-System Programming       11–2         Interrupting In-System Programming       11–3         Voltage Suppression Programming       11–3         Vocto Powered before V <sub>CENT</sub> 11–3         VO Fins Tri-Stated during In-System Programming       11–4         IEEE Std. 1149.1 Signals       11–4         Programming via a Download Cable       11–5         Disabling IEEE Std. 1149.1 Circuitry       11–5         Working with Different Voltage Levels       11–6         Sequential Programming       11–6         Sequential Programming       11–6         Sequential Programming       11–6         Sequential Programming       11–6         Sequential Programmi                                                                              |                                                                    |      |

| Referenced Documents       10-11         Document Revision History       10-12         Section IV. In-System Programmability       IV-1         Section IV. In-System Programmability Guidelines for MAX II Devices       IV-1         Chapter 11. In-System Programmability Guidelines for MAX II Devices       11-1         General ISP Guidelines       11-1         Operating Conditions       11-1         Introduction       11-1         Input Voltage       11-2         UFM Operations During In-System Programming       11-3         MultiVolt Devices and Power-Up Sequences       11-3         V <sub>CCIO</sub> Powered before V <sub>CCINT</sub> 11-3         V <sub>CCIO</sub> Powered before V <sub>CCINT</sub> 11-3         V <sub>CCIO</sub> Powered before V <sub>CCINT</sub> 11-4         TCK Signal       11-4         Programming via a Download Cable       11-4         Programming via a Download Cable       11-5         Disabling IEEE Std. 1149.1 Circuitry       11-5         Working with Different Voltage Levels       11-6         Sequential Programming       11-6 </td <td></td> <td></td> |                                                                    |      |

| Document Revision History       10–12         Section IV. In-System Programmability       IV-1         Chapter 11. In-System Programmability Guidelines for MAX II Devices       11–1         Introduction       11–1         Operating Conditions       11–1         Operating Conditions       11–1         Input Voltage       11–1         UFM Operations During In-System Programming       11–2         Interrupting In-System Programming       11–3         MultiVolt Devices and Power-Up Sequences       11–3         V <sub>CCD</sub> Powerdo Before V <sub>CCNT</sub> 11–3         I/O Pins Tri-Stated during In-System Programming       11–4         TCK Signal       11–4         Programming via a Download Cable       11–4         Programming via a Download Cable       11–5         Working with Different Voltage Levels       11–5         Sequential Programming       11–6         Sequential Programming       11–6         Sequential Programming       11–6         Sequential Programming       11–5         Working with Different Voltage Levels       11–6         Sequential Programming       11–6         Sequential Programming       11–6         Sequential Programming       11–6         Sequ                                                                    |                                                                    |      |

| Section IV. In-System Programmability       IV-1         Chapter 11. In-System Programmability Guidelines for MAX II Devices       11-1         Introduction       11-1         General ISP Guidelines       11-1         Operating Conditions       11-1         Input Voltage       11-1         Input Voltage       11-2         UFM Operations During In-System Programming       11-2         Interrupting In-System Programming       11-2         Interrupting In-System Programming       11-3         V <sub>CC0</sub> Powered before V <sub>CENT</sub> 11-3         J/O Pins Tri-Stated during In-System Programming       11-4         TCK Signal       11-4         Programming via a Download Cable       11-5         Disabling IEEE Std. 1149.1 Circuitry       11-5         Working with Different Voltage Levels       11-6         Sequential Versus Concurrent Programming       11-6         Sequential Different Voltage Levels       11-6         Sequential Different Voltage Levels       11-7         Invalid ID and Unrecognized Device Messages       11-7                       |                                                                    |      |

| Revision History       IV-1         Chapter 11. In-System Programmability Guidelines for MAX II Devices       Introduction         Introduction       11-1         General ISP Guidelines       11-1         Operating Conditions       11-1         IsP Voltage       11-1         Input Voltages       11-2         UFM Operations During In-System Programming       11-2         Interrupting In-System Programming       11-3         MultiVolt Devices and Power-Up Sequences       11-3         V <sub>CCI0</sub> Powered before V <sub>CCNT</sub> 11-3         I/O Pins Tri-Stated during In-System Programming       11-4         Pull-Up and Pull-Down of JTAG Pins During In-System Programming       11-4         TCK Signal       11-4         Programming via a Download Cable       11-4         Programming via a Download Cable       11-5         Disabling IEEE Std. 1149.1 Circuitry       11-5         Disabling Guidelines       11-6         Sequential Versus Concurrent Programming       11-6         Sequential Versus Concurrent Programming       11-6         Sequential Programming       11-6         Sequential Programming       11-6         Sequential Programming       11-7         Invalid ID and Unrecognized Device Messages <td></td> <td></td>                |                                                                    |      |

| Chapter 11. In-System Programmability Guidelines for MAX II Devices         Introduction       11-1         General ISP Guidelines       11-1         Operating Conditions       11-1         IsP Voltage       11-1         Input Voltages       11-2         UFM Operations During In-System Programming       11-2         Interrupting In-System Programming       11-3         MultiVolt Devices and Power-Up Sequences       11-3         V <sub>CCIO</sub> Powered before V <sub>CCINT</sub> 11-3         I/O Pins Tri-Stated during In-System Programming       11-4         IEEE Std. 1149.1 Signals       11-4         TCK Signal       11-4         Programming via a Download Cable       11-5         Disabling IEEE Std. 1149.1 Circuitry       11-5         Working with Different Voltage Levels       11-6         Sequential Programming       11-6         Sequential Programming       11-6         Sequential Programming       11-6         Sequential Programming       11-7         Into Subleshooting Guidelines       11-7         Notity Circuitry       11-5         Working with Different Voltage Levels       11-6         Sequential Programming       11-6         Sequential Programming                                                                               |                                                                    |      |

| Introduction11-1General ISP Guidelines11-1Operating Conditions11-1ISP Voltage11-1Input Voltages11-2UFM Operations During In-System Programming11-3MultiVolt Devices and Power-Up Sequences11-3 $V_{CCIO}$ Powered before $V_{CCINT}$ 11-3I/O Pins Tri-Stated during In-System Programming11-3J/O Pins Tri-Stated during In-System Programming11-3Pull-Up and Pull-Down of JTAG Pins During In-System Programming11-4TCK Signal11-4Programming via a Download Cable11-5Disabling IEEE Std. 1149.1 Circuitry11-5Working with Different Voltage Levels11-6Sequential Versus Concurrent Programming11-6Sequential Versus Concurrent Programming11-6ISP Troubleshooting Guidelines11-7Invalid ID and Unrecognized Device Messages11-7Download Cable Connected Incorrectly11-7TDO Is Not Connected11-8Incomplete JTAG Chain11-8Noisy TCK Signal11-8Jam Player Ported Incorrectly11-8Incomplete JTAG Chain11-8Noisy TCK Signal11-9Software Issues11-9Software Issues11-9Software Issues11-9Prover-Up Problems11-9Porting the Jam Player11-4Processor and Memory Requirements11-9Porting the Jam Player11-4Proversup Problems11-9Porting the Jam Player1                                                                                                                                                         | Revision History                                                   | IV–1 |

| Introduction11-1General ISP Guidelines11-1Operating Conditions11-1ISP Voltage11-1Input Voltages11-2UFM Operations During In-System Programming11-3MultiVolt Devices and Power-Up Sequences11-3 $V_{CCIO}$ Powered before $V_{CCINT}$ 11-3I/O Pins Tri-Stated during In-System Programming11-3J/O Pins Tri-Stated during In-System Programming11-3Pull-Up and Pull-Down of JTAG Pins During In-System Programming11-4TCK Signal11-4Programming via a Download Cable11-5Disabling IEEE Std. 1149.1 Circuitry11-5Working with Different Voltage Levels11-6Sequential Versus Concurrent Programming11-6Sequential Versus Concurrent Programming11-6ISP Troubleshooting Guidelines11-7Invalid ID and Unrecognized Device Messages11-7Download Cable Connected Incorrectly11-7TDO Is Not Connected11-8Incomplete JTAG Chain11-8Noisy TCK Signal11-8Jam Player Ported Incorrectly11-8Incomplete JTAG Chain11-8Noisy TCK Signal11-9Software Issues11-9Software Issues11-9Software Issues11-9Prover-Up Problems11-9Porting the Jam Player11-4Processor and Memory Requirements11-9Porting the Jam Player11-4Proversup Problems11-9Porting the Jam Player1                                                                                                                                                         | Chantay 11 In System Dragrammability Guidalinas for MAY II Daviasa |      |

| General ISP Guidelines11-1Operating Conditions11-1ISP Voltage11-2Input Voltages11-2UFM Operations During In-System Programming11-2Interrupting In-System Programming11-3MultiVolt Devices and Power-Up Sequences11-3V_CCIO Powered before V_CCINT11-3I/O Pins Tri-Stated during In-System Programming11-3Pull-Up and Pull-Down of JTAG Pins During In-System Programming11-4IEEE Std. 1149.1 Signals11-4TCK Signal11-4Programming via a Download Cable11-5Disabling IEEE Std. 1149.1 Circuitry11-5Working with Different Voltage Levels11-6Sequential Programming11-6Sequential Programming11-6ISP Troubleshooting Guidelines11-7Invalid ID and Unrecognized Device Messages11-7Download Cable Connected Incorrectly11-7TDO Is Not Connected Incorrectly11-8Noisy TCK Signal11-8Incomplete JTAG Chain11-8Noisy TCK Signal11-8Incomplete JTAG Chain Continuity11-8Verify the JTAG Chain Continuity11-8Check the V <sub>CC</sub> Level of the Board During In-System Programming11-9Software Issues11-9Software Issues11-9Powing Male on JTAG Pins11-9Porting the Jam Player11-9Porting the Jam Player11-9Porting the Jam Player11-9Software Issues11-9Software Issu                                                                                                                                       |                                                                    | 11 1 |

| $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |      |

| ISP Voltage11-1Input Voltages11-2UFM Operations During In-System Programming11-2UITHTrupting In-System Programming11-3MultiVolt Devices and Power-Up Sequences11-3V <sub>CCIO</sub> Powered before V <sub>CCNT</sub> 11-3I/O Pins Tri-Stated during In-System Programming11-3Pull-Up and Pull-Down of JTAG Pins During In-System Programming11-4IEEE Std. 1149.1 Signals11-4TCK Signal11-4Programming via a Download Cable11-5Disabling IEEE Std. 1149.1 Circuitry11-5Working with Different Voltage Levels11-6Sequential Versus Concurrent Programming11-6Sequential Programming11-6Sequential Programming11-6Sequential Programming11-6Sequential Versus Concurrent Programming11-7Invalid ID and Unrecognized Device Messages11-7Invalid ID and Unrecognized Device Messages11-7Invalid ID and Cable Connected Incorrectly11-8Incomplete JTAG Chain11-8Incomplete JTAG Chain11-8Verify the JTAG Chain Continuity11-8Verify the JTAG Chain Continuity11-8Verify the JTAG Chain Continuity11-9Power-Up Problems11-9Software Issues11-9Software Issues11-9Software Issues11-9Processor and Memory Requirements11-9Proting the Jam Player11-10                                                                                                                                                            |                                                                    |      |

| Input Voltages11-2UFM Operations During In-System Programming11-2Interrupting In-System Programming11-3MultiVolt Devices and Power-Up Sequences11-3V <sub>CCIO</sub> Powered before V <sub>CCINT</sub> 11-3I/O Pins Tri-Stated during In-System Programming11-3Pull-Up and Pull-Down of JTAG Pins During In-System Programming11-4IEEE Std. 1149.1 Signals11-4TCK Signal11-4TCK Signal11-5Disabiling IEEE Std. 1149.1 Circuitry11-5Working with Different Voltage Levels11-6Sequential Programming11-6Sequential Programming11-6Sequential Programming11-6Sequential Programming11-6Sequential Programming11-6Sequential Programming11-6Sequential Programming11-7Invalid ID and Unrecognized Device Messages11-7TDO Is Not Connected Incorrectly11-8Incomplete JTAG Chain11-8Noisy TCK Signal11-8Incomplete JTAG Chain11-8Verify the JTAG Chain Continuity11-8Verify the JTAG Chain Continuity11-8Check the V <sub>CC</sub> Level of the Board During In-System Programming11-9Software Issues11-9Software Issues11-9Protessor and Memory Requirements11-9Porting the Jam Player11-10                                                                                                                                                                                                                   | Operating Conditions                                               |      |

| UFM Operations During In-System Programming11–2Interrupting In-System Programming11–3MultiVolt Devices and Power-Up Sequences11–3V <sub>CCO</sub> Powered before V <sub>CCNT</sub> 11–3I/O Pins Tri-Stated during In-System Programming11–3Pull-Up and Pull-Down of JTAG Pins During In-System Programming11–4IEEE Std. 1149.1 Signals11–4TCK Signal11–4TCK Signal11–5Disabling IEEE Std. 1149.1 Circuitry11–5Working with Different Voltage Levels11–6Sequential Vergramming11–6Sequential Vergramming11–6Concurrent Programming11–6Sequential Vergramming11–6Sequential Vergramming11–6Nowaload Cable Connected Incorrectly11–7Invalid ID and Unrecognized Device Messages11–7TDO Is Not Connected11–8Incomplete JTAG Chain11–8Noisy TCK Signal11–8Jam Player Ported Incorrectly11–8Verify the JTAG Chain Continuity11–8Verify the JTAG Chain Continuity11–8Power-Up Problems11–9Software Issues11–9Software Issues11–9Processor and Memory Requirements11–9Proting the Jam Player11–10                                                                                                                                                                                                                                                                                                                |                                                                    |      |

| Interrupting In-System Programming11–3MultiVolt Devices and Power-Up Sequences11–3 $V_{CCIO}$ Powered before $V_{CCINT}$ 11–3I/O Pins Tri-Stated during In-System Programming11–3Pull-Up and Pull-Down of JTAG Pins During In-System Programming11–4IEEE Std. 1149.1 Signals11–4TCK Signal11–4Programming via a Download Cable11–5Disabling IEEE Std. 1149.1 Circuitry11–5Working with Different Voltage Levels11–6Sequential Programming11–6Sequential Programming11–6Sequential Programming11–6Sequential Programming11–6Sequential Programming11–6Sequential Programming11–7Invalid ID and Unrecognized Device Messages11–7Download Cable Connected Incorrectly11–7TDO Is Not Connected Incorrectly11–8Incomplete JTAG Chain11–8Noisy TCK Signal11–8Verify the JTAG Chain Continuity11–8Verify the JTAG Chain Continuity11–8Check the $V_{Cc}$ Level of the Board During In-System Programming11–9Random Signals on JTAG Pins11–9Software Issues11–9Protessor and Memory Requirements11–9Proting the Jam Player11–9Proting the Jam Player11–9Porting the Jam Player11–9Porting the Jam Player11–9                                                                                                                                                                                                     |                                                                    |      |

| MultiVolt Devices and Power-Up Sequences11–3 $V_{CCIO}$ Powered before $V_{CCINT}$ 11–3 $I/O$ Pins Tri-Stated during In-System Programming11–3Pull-Up and Pull-Down of JTAG Pins During In-System Programming11–4IEEE Std. 1149.1 Signals11–4TCK Signal11–4TCK Signal11–4Programming via a Download Cable11–5Disabling IEEE Std. 1149.1 Circuitry11–5Working with Different Voltage Levels11–6Sequential versus Concurrent Programming11–6Sequential Programming11–6Sequential Programming11–6Sequential Drogramming11–6Sequential Drogramming11–7Invalid ID and Unrecognized Device Messages11–7Download Cable Connected Incorrectly11–8Incomplete JTAG Chain11–8Noisy TCK Signal11–8Verify the JTAG Chain Continuity11–8Verify the JTAG Chain Continuity11–8Check the $V_{cc}$ Level of the Board During In-System Programming11–9Power-Up Problems11–9Random Signals on JTAG Pins11–9Software Issues11–9Processor and Memory Requirements11–9Porting the Jam Player11–10                                                                                                                                                                                                                                                                                                                              |                                                                    |      |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |      |

| I/O Pins Tri-Stated during In-System Programming11–3Pull-Up and Pull-Down of JTAG Pins During In-System Programming11–4IEEE Std. 1149.1 Signals11–4TCK Signal11–4Programming via a Download Cable11–5Disabling IEEE Std. 1149.1 Circuitry11–5Working with Different Voltage Levels11–6Sequential versus Concurrent Programming11–6Sequential Programming11–6Sequential Programming11–6Sequential Programming11–6Sequential Programming11–7Invalid ID and Unrecognized Device Messages11–7Download Cable Connected Incorrectly11–7TDO Is Not Connected11–8Incomplete JTAG Chain11–8Noisy TCK Signal11–8Jam Player Ported Incorrectly11–8Verify the JTAG Chain Continuity11–8Check the $V_{cc}$ Level of the Board During In-System Programming11–9Power-Up Problems11–9Software Issues11–9Software Issues11–9Processor and Memory Requirements11–9Porting the Jam Player11–9Porting the Jam Player11–9                                                                                                                                                                                                                                                                                            |                                                                    |      |

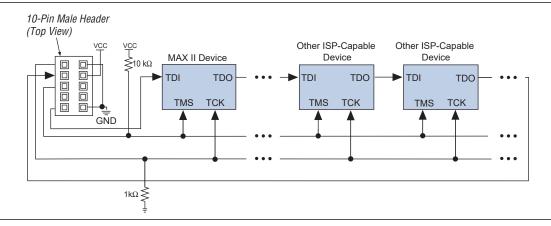

| Pull-Up and Pull-Down of JTAG Pins During In-System Programming11-4IEEE Std. 1149.1 Signals11-4TCK Signal11-4Programming via a Download Cable11-5Disabling IEEE Std. 1149.1 Circuitry11-5Working with Different Voltage Levels11-6Sequential versus Concurrent Programming11-6Sequential Programming11-6Sequential Versus Concurrent Programming11-6Sequential Versus Concurrent Programming11-6Sequential Versus Concurrent Programming11-6Sequential Drogramming11-7Invalid ID and Unrecognized Device Messages11-7Download Cable Connected Incorrectly11-7TDO Is Not Connected11-8Incomplete JTAG Chain11-8Noisy TCK Signal11-8Jam Player Ported Incorrectly11-8Verify the JTAG Chain Continuity11-8Check the $V_{cc}$ Level of the Board During In-System Programming11-9Power-Up Problems11-9Software Issues11-9Software Issues11-9Software Issues11-9Processor and Memory Requirements11-9Porting the Jam Player11-9Porting the Jam Player11-9                                                                                                                                                                                                                                                                                                                                                     |                                                                    |      |

| IEEE Std. 1149.1 Signals11-4TCK Signal11-4Programming via a Download Cable11-5Disabling IEEE Std. 1149.1 Circuitry11-5Working with Different Voltage Levels11-6Sequential versus Concurrent Programming11-6Sequential Programming11-6Concurrent Programming11-6ISP Troubleshooting Guidelines11-7Invalid ID and Unrecognized Device Messages11-7Download Cable Connected Incorrectly11-7TDO Is Not Connected11-8Noisy TCK Signal11-8Jam Player Ported Incorrectly11-8Verify the JTAG Chain11-8Verify the JTAG Chain Continuity11-8Check the $V_{CC}$ Level of the Board During In-System Programming11-9Random Signals on JTAG Pins11-9Software Issues11-9SP via Embedded Processors11-9Processor and Memory Requirements11-9Porting the Jam Player11-9Porting the Jam Player11-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |      |

| Programming via a Download Cable11–5Disabling IEEE Std. 1149.1 Circuitry11–5Working with Different Voltage Levels11–6Sequential versus Concurrent Programming11–6Sequential Programming11–6Gequential Programming11–6Concurrent Programming11–6ISP Troubleshooting Guidelines11–7Invalid ID and Unrecognized Device Messages11–7Download Cable Connected Incorrectly11–7TDO Is Not Connected11–8Incomplete JTAG Chain11–8Noisy TCK Signal11–8Jam Player Ported Incorrectly11–8Verify the JTAG Chain Continuity11–8Verify the JTAG Chain Continuity11–9Power-Up Problems11–9Software Issues11–9Software Issues11–9Processor and Memory Requirements11–9Porting the Jam Player11–9Porting the Jam Player11–9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                    |      |

| Disabling IEEE Std. 1149.1 Circuitry11–5Working with Different Voltage Levels11–6Sequential versus Concurrent Programming11–6Sequential Programming11–6Concurrent Programming11–6Goncurrent Programming11–6ISP Troubleshooting Guidelines11–7Invalid ID and Unrecognized Device Messages11–7Download Cable Connected Incorrectly11–7TDO Is Not Connected11–8Incomplete JTAG Chain11–8Jam Player Ported Incorrectly11–8Verify the JTAG Chain Continuity11–8Verify the JTAG Chain Continuity11–8Verify the JTAG Chain Continuity11–9Power-Up Problems11–9Software Issues11–9Software Issues11–9Software Issues11–9Processor and Memory Requirements11–9Porting the Jam Player11–9Porting the Jam Player11–9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |      |

| Working with Different Voltage Levels11-6Sequential versus Concurrent Programming11-6Sequential Programming11-6Concurrent Programming11-6ISP Troubleshooting Guidelines11-7Invalid ID and Unrecognized Device Messages11-7Download Cable Connected Incorrectly11-7TDO Is Not Connected11-8Incomplete JTAG Chain11-8Noisy TCK Signal11-8Jam Player Ported Incorrectly11-8Verify the JTAG Chain Continuity11-8Verify the JTAG Chain Continuity11-9Power-Up Problems11-9Software Issues11-9Software Issues11-9Processor and Memory Requirements11-9Porting the Jam Player11-9Porting the Jam Player11-9Porting the Jam Player11-9ISP via Embedded Processors11-9Porting the Jam Player11-9Porting the Jam Player11-9Porting the Jam Player11-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                    |      |

| Sequential versus Concurrent Programming11-6Sequential Programming11-6Concurrent Programming11-6ISP Troubleshooting Guidelines11-7Invalid ID and Unrecognized Device Messages11-7Download Cable Connected Incorrectly11-7TDO Is Not Connected11-8Incomplete JTAG Chain11-8Jam Player Ported Incorrectly11-8Troubleshooting Tips11-8Verify the JTAG Chain Continuity11-8Check the $V_{\rm CC}$ Level of the Board During In-System Programming11-9Power-Up Problems11-9Software Issues11-9Software Issues11-9Processor and Memory Requirements11-9Porting the Jam Player11-9Porting the Jam Player11-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |      |

| Sequential Programming11-6Concurrent Programming11-6ISP Troubleshooting Guidelines11-7Invalid ID and Unrecognized Device Messages11-7Download Cable Connected Incorrectly11-7TDO Is Not Connected11-8Incomplete JTAG Chain11-8Jam Player Ported Incorrectly11-8Troubleshooting Tips11-8Verify the JTAG Chain Continuity11-8Check the $V_{cc}$ Level of the Board During In-System Programming11-9Power-Up Problems11-9Software Issues11-9Software Issues11-9Processor and Memory Requirements11-9Porting the Jam Player11-9Porting the Jam Player11-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |      |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Sequential versus Concurrent Programming                           |      |

| ISP Troubleshooting Guidelines       11–7         Invalid ID and Unrecognized Device Messages       11–7         Download Cable Connected Incorrectly       11–7         TDO Is Not Connected       11–8         Incomplete JTAG Chain       11–8         Noisy TCK Signal       11–8         Jam Player Ported Incorrectly       11–8         Troubleshooting Tips       11–8         Verify the JTAG Chain Continuity       11–8         Check the V <sub>CC</sub> Level of the Board During In-System Programming       11–9         Power-Up Problems       11–9         Software Issues       11–9         ISP via Embedded Processors       11–9         Processor and Memory Requirements       11–9         Porting the Jam Player       11–9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Sequential Programming                                             |      |

| Invalid ID and Unrecognized Device Messages11–7Download Cable Connected Incorrectly11–7TDO Is Not Connected11–8Incomplete JTAG Chain11–8Noisy TCK Signal11–8Jam Player Ported Incorrectly11–8Troubleshooting Tips11–8Verify the JTAG Chain Continuity11–8Check the V <sub>CC</sub> Level of the Board During In-System Programming11–9Power-Up Problems11–9Software Issues11–9ISP via Embedded Processors11–9Processor and Memory Requirements11–9Porting the Jam Player11–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Concurrent Programming                                             |      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ISP Troubleshooting Guidelines                                     |      |

| TDO Is Not Connected11–8Incomplete JTAG Chain11–8Noisy TCK Signal11–8Jam Player Ported Incorrectly11–8Troubleshooting Tips11–8Verify the JTAG Chain Continuity11–8Check the V <sub>CC</sub> Level of the Board During In-System Programming11–9Power-Up Problems11–9Software Issues11–9Software Issues11–9Processor and Memory Requirements11–9Porting the Jam Player11–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Invalid ID and Unrecognized Device Messages                        |      |

| Incomplete JTAG Chain11–8Noisy TCK Signal11–8Jam Player Ported Incorrectly11–8Troubleshooting Tips11–8Verify the JTAG Chain Continuity11–8Check the V <sub>CC</sub> Level of the Board During In-System Programming11–9Power-Up Problems11–9Software Issues11–9ISP via Embedded Processors11–9Porcessor and Memory Requirements11–9Porting the Jam Player11–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Download Cable Connected Incorrectly                               |      |

| Noisy TCK Signal       11–8         Jam Player Ported Incorrectly       11–8         Troubleshooting Tips       11–8         Verify the JTAG Chain Continuity       11–8         Check the V <sub>CC</sub> Level of the Board During In-System Programming       11–9         Power-Up Problems       11–9         Software Issues       11–9         ISP via Embedded Processors       11–9         Processor and Memory Requirements       11–9         Porting the Jam Player       11–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TDO Is Not Connected                                               |      |

| Jam Player Ported Incorrectly       11–8         Troubleshooting Tips       11–8         Verify the JTAG Chain Continuity       11–8         Check the V <sub>CC</sub> Level of the Board During In-System Programming       11–9         Power-Up Problems       11–9         Random Signals on JTAG Pins       11–9         Software Issues       11–9         ISP via Embedded Processors       11–9         Processor and Memory Requirements       11–9         Porting the Jam Player       11–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Incomplete JTAG Chain                                              |      |

| Troubleshooting Tips       11–8         Verify the JTAG Chain Continuity       11–8         Check the V <sub>CC</sub> Level of the Board During In-System Programming       11–9         Power-Up Problems       11–9         Random Signals on JTAG Pins       11–9         Software Issues       11–9         ISP via Embedded Processors       11–9         Processor and Memory Requirements       11–9         Porting the Jam Player       11–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Noisy TCK Signal                                                   |      |

| Verify the JTAG Chain Continuity       11–8         Check the V <sub>CC</sub> Level of the Board During In-System Programming       11–9         Power-Up Problems       11–9         Random Signals on JTAG Pins       11–9         Software Issues       11–9         ISP via Embedded Processors       11–9         Processor and Memory Requirements       11–9         Porting the Jam Player       11–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Jam Player Ported Incorrectly                                      |      |

| Verify the JTAG Chain Continuity       11–8         Check the V <sub>CC</sub> Level of the Board During In-System Programming       11–9         Power-Up Problems       11–9         Random Signals on JTAG Pins       11–9         Software Issues       11–9         ISP via Embedded Processors       11–9         Processor and Memory Requirements       11–9         Porting the Jam Player       11–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |      |

| Check the V <sub>CC</sub> Level of the Board During In-System Programming       11–9         Power-Up Problems       11–9         Random Signals on JTAG Pins       11–9         Software Issues       11–9         ISP via Embedded Processors       11–9         Processor and Memory Requirements       11–9         Porting the Jam Player       11–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                    |      |

| Power-Up Problems       11–9         Random Signals on JTAG Pins       11–9         Software Issues       11–9         ISP via Embedded Processors       11–9         Processor and Memory Requirements       11–9         Porting the Jam Player       11–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |      |

| Random Signals on JTAG Pins       11–9         Software Issues       11–9         ISP via Embedded Processors       11–9         Processor and Memory Requirements       11–9         Porting the Jam Player       11–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |      |

| Software Issues       11–9         ISP via Embedded Processors       11–9         Processor and Memory Requirements       11–9         Porting the Jam Player       11–10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |      |